当地时间4月23日,台积电在美国召开“2025年北美技术研讨会”。此次会议台积电介绍了先进技术发展及行业挑战与机遇,重点分析了AI驱动的半导体技术升级、先进制程路线图、下一代节点验证及晶体管架构与材料创新,旨在支撑未来智能计算基础设施。

以下为该会议的重点内容。

AI与半导体市场

根据台积电发布的最新信息,半导体行业正进入一个前所未有的扩张阶段,预计到2030年,全球半导体市场规模将达到1万亿美元。推动这一增长的最重要因素是高性能计算(HPC)和人工智能(AI)应用的爆发式发展。

上图显示,台积电预测,到2030年,HPC/AI将占全球半导体市场的45%,成为主导应用平台。其次是智能手机,占25%;汽车电子占15%;物联网占10%;其他领域占5%。这种市场结构的变化表明,半导体市场正从以移动设备需求为中心,关键转变为以AI和高吞吐量计算工作负载为核心的创新驱动模式。

AI驱动的应用如何迅速加速对半导体的需求?从数据中心的AI加速器开始,这种增长扩展到AI个人电脑、AI智能手机、增强现实/虚拟现实(AR/XR)设备,以及更长期的应用,如自动驾驶出租车和人形机器人。这些应用不仅在数量上不断增加,架构复杂度也在不断提升。

具体而言,预计到2029年,AI个人电脑的出货量将达到2.8亿台,而AI智能手机的出货量最早在2025年就有望突破10亿部。预计到2028年,AR/XR设备的出货量将达到5000万台。

此外,像自动驾驶出租车和人形机器人这样的下一代应用,预计到2030年,每年各自将需要250万个高性能芯片。这些数据表明,未来的芯片不仅要具备更高的计算性能,还需要在能源效率、系统级集成和封装密度方面取得突破。

台积电认为,这些新兴的AI驱动应用将大幅增加芯片的复杂性,对更紧密的集成提出更高要求,并推动制程创新,最终为半导体行业的新一轮增长提供动力。在台积电看来,这是实现1万亿美元半导体产业愿景的基本路径。

先进制程技术:N3、N2、A16、A14

N3

目前,台积电的N3系列(即3nm工艺)已包含已量产的N3和N3E,并计划后续推出N3P、N3X、N3A以及N3C等版本。

台积电透露,公司计划于2024年第四季度开始生产基于性能增强型N3P(第三代3纳米级)工艺技术的芯片。N3P是N3E的后续产品,主要面向需要增强性能并保留3纳米级IP的客户端和数据中心应用。

台积电的N3P是N3E的光学微缩工艺,它保留了设计规则和 IP 兼容性,同时在相同漏电流下性能提升 5%,或在相同频率下功耗降低 5% 至 10%,并且对于典型的逻辑、SRAM 和模拟模块混合设计,晶体管密度提升 4%。由于 N3P 的密度增益源于改进的光学器件,它能够在所有芯片结构上实现更好的扩展,尤其有利于大量使用 SRAM 的高性能设计。N3P 现已投入生产,因此该公司目前正在为其主要客户基于该技术开发产品。

与N3P 相比,N3X 有望在相同功率下将最大性能提高 5%,或在相同频率下将功耗降低 7%。然而,与 N3P 相比,N3X 的主要优势在于它支持高达 1.2V 的电压(对于 3nm 级技术来说,这是极限值),这将为需要它的应用程序(即客户端 CPU)提供绝对最大频率 (Fmax)。Fmax 的代价是:漏电功率高达 250%——因此,芯片开发人员在构建基于 N3X 且电压为 1.2V 的设计时必须小心谨慎。 N3X芯片预计将于今年下半年实现量产。

台积电路线图有一些细微的变化。路线图已延长至2028年,增加了N3C和A14。N3C是一个压缩版本,这意味着良率学习曲线已经到了可以进一步优化工艺密度的阶段。

台积电会上披露了其下一代芯片制造工艺的进展。公司预计将在今年下半年开始量产N2芯片。这是台积电首次采用全环绕栅极(GAA)纳米片晶体管技术进行生产。

N2

N2(即2nm工艺)作为台积电全新的工艺技术,采用了纳米片或环绕栅极设计。相比前代技术,N2能够在相同功耗下实现10%-15%的速度提升,或者在相同速度下降低20%-30%的功耗。

与现有的N3E工艺相比,N2工艺的性能提升了10%-15%,功耗降低了25%-30%,同时晶体管密度增加了15%。台积电还透露,N2的晶体管性能已接近预期目标,256Mb SRAM模块的平均良率超过90%。随着N2逐渐进入量产阶段,其工艺成熟度也将进一步提高。台积电预计,在智能手机和高性能计算应用的推动下,2nm技术的流片数量在投产初期将超过3nm和5nm技术。

此外,台积电继续遵循其技术改进战略,推出了N2P作为N2系列的延伸。N2P在N2的基础上进一步优化了性能和功耗表现,计划于2026年投入生产。在N2之后,台积电将进入A16(即1.6nm)节点。

A16

A16工艺的核心技术特点之一是超级电轨架构,也称为背面供电技术。通过将供电网络移至晶圆背面,这种技术能够释放更多正面布局空间,从而提升芯片的逻辑密度和整体效能。据台积电介绍,与N2P相比,A16在相同电压和设计条件下可实现8%-10%的性能提升;在相同频率和晶体管数量下,功耗则能降低15%-20%,密度提升范围为1.07-1.10倍。

台积电特别指出,A16工艺特别适合用于信号路由复杂且供电网络密集的高性能计算(HPC)产品。按照计划,A16将于2026年下半年开始量产。

A14

全新A14制程技术的推出是此次研讨会的一大亮点。A14制程是基于台积电领先业界N2(2nm)制程的重大进展,基于第二代GAA晶体管技术(NanoFLEX晶体管架构),提供更快计算和更佳能源效率推动人工智能(AI)转型,亦有望增进端侧AI功能,强化智能手机等应用。根据规划,A14预计将于2028年开始量产,截至目前进度顺利,良率表现优于预期。

先进封装与系统集成创新

在先进封装领域,台积电也有多项重要信息公布。

台积电推出了3DFabric平台,这是一套全面的2.5D和3D集成技术,包括CoWoS(Chip-on-Wafer-on-Substrate,晶圆上芯片再到基板)、InFO(Integrated Fan-Out,集成扇出)和SoIC(System on Integrated Chips,集成芯片系统)。这些平台旨在克服传统单片设计的扩展限制,支持基于小芯片的架构、高带宽内存集成和异构系统优化。

左侧是堆叠或芯片级/晶圆级集成的选项。SoIC-P采用微凸块技术,可将间距降至 16 微米。使用无凸块技术(SoIC-X),可以实现几微米的间距。台积电最初采用 9 微米工艺,目前已投入 6 微米量产,并将进一步改进,从而实现类似单片的集成密度。

对于2.5/3D 集成,有很多选择。晶圆上芯片 (CoWoS) 技术既支持常见的硅中介层,也支持 CoWoS-L,后者使用带有局部硅桥的有机中介层实现高密度互连。CoWos-R 则提供纯有机中介层。

集成扇出(InFO) 技术于 2016 年首次应用于移动应用。该平台现已扩展至支持汽车应用。

自2020年以来,台积电的晶圆系统集成技术(InFO-SoW)已成功应用于如Cerebras和特斯拉等公司的尖端产品中,其中特斯拉的Dojo超级计算机所搭载的晶圆级处理器就是这一技术的标志性产物。晶圆级设计通过直接在整片硅晶圆上构建处理器,实现了前所未有的核心间通信速度、性能密度以及能效,然而,其复杂度与成本也相应增加,限制了广泛应用。

还有更新的晶圆系统(TSMC-SoW) 封装。这项技术将集成规模拓展至晶圆级。其中一种是先芯片 (SoW-P) 方法,即将芯片放置在晶圆上,然后构建集成式 RDL 将芯片连接在一起。另一种是后芯片 (SoW-X) 方法,即先在晶圆级构建中介层,然后将芯片放置在晶圆上。最后一种方法可以实现比标准光罩尺寸大 40 倍的设计。

台积电的SoIC(集成芯片系统)技术在延续摩尔定律方面发挥了关键作用,它不是通过传统的单片缩放,而是采用基于小芯片的架构,结合高密度3D异构集成。作为台积电3DFabric平台的基石之一,SoIC实现了无基板3D堆叠,允许不同节点、功能和材料的裸片通过高密度互连进行垂直集成。

台积电提供的图表还展示了当今典型的人工智能加速器应用,该应用通过硅中介层将单片SoC与HBM存储器堆栈集成在一起。

台积介绍了其它一系列高性能集成解决方案,包括用于HBM4 的 N12 和N3 制程逻辑基础裸晶(Base Die)、运用 COUPE 紧凑型通用光子引擎技术的 SiPh 硅光子整合。

特别是在内存集成方面,台积电特别强调了CoW-SoW在结合HBM4(第四代高带宽内存)上的潜力。HBM4凭借其2048位的超宽接口,有望通过与逻辑芯片的紧密集成,解决AI及HPC工作负载对高带宽、低延迟内存的迫切需求。这种集成方式不仅极大提升了数据传输速度,还有效降低了功耗,为持续增长的计算密集型应用提供了理想的解决方案。

关于功率优化,未来的AI加速器可能需要数千瓦的功率,这对封装内的功率传输提出了巨大的挑战。集成稳压器将有助于解决此类问题。台积电开发了一种高密度电感器,这是开发此类稳压器所需的关键组件。因此,单片PMIC加上该电感器可以提供5倍的功率传输密度(相对于PCB级)。

未来应用展望

此外,还有很多创新的应用也需要先进封装技术的支持。

增强现实眼镜就是一个新产品的例子,这类设备需要的组件包括超低功耗处理器、用于 AR 感知的高分辨率摄像头、用于代码存储的嵌入式非易失性存储器 (eNVM)、用于空间计算的大型主处理器、近眼显示引擎、用于低延迟射频的 WiFi/蓝牙,以及用于低功耗充电的数字密集型电源管理集成电路 (PMIC)。这类产品将为复杂性和效率设定新的标准。

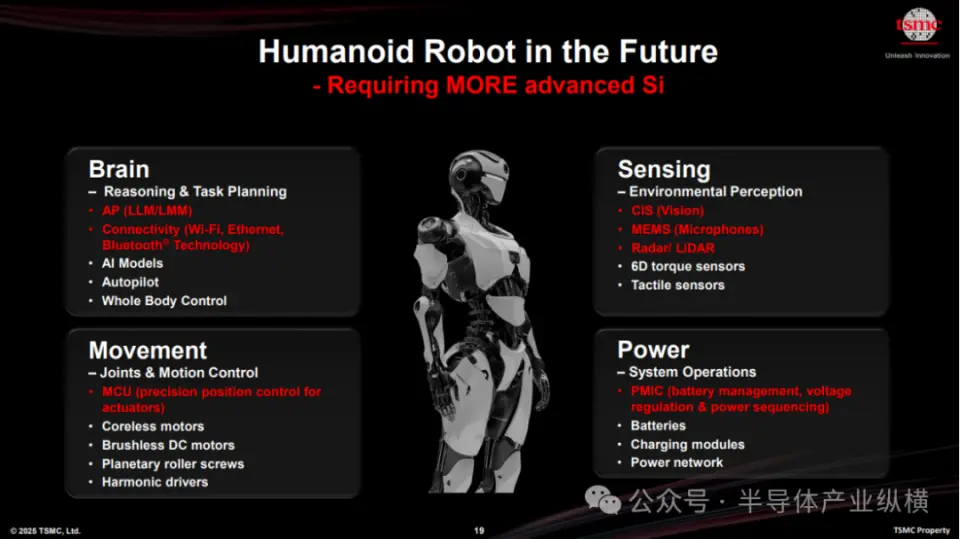

虽然自动驾驶汽车备受关注,但人形机器人的需求也备受关注。其需要大量先进硅片。而将所有这些芯片集成到高密度、高能效的封装中的能力也至关重要。